ASML planuje szerokie zastosowanie technologii High‑NA EUV już w przyszłym roku do produkcji układów scalonych z rozmiarem tranzystorów 1,4 nm i mniejszym.

Krótka treść

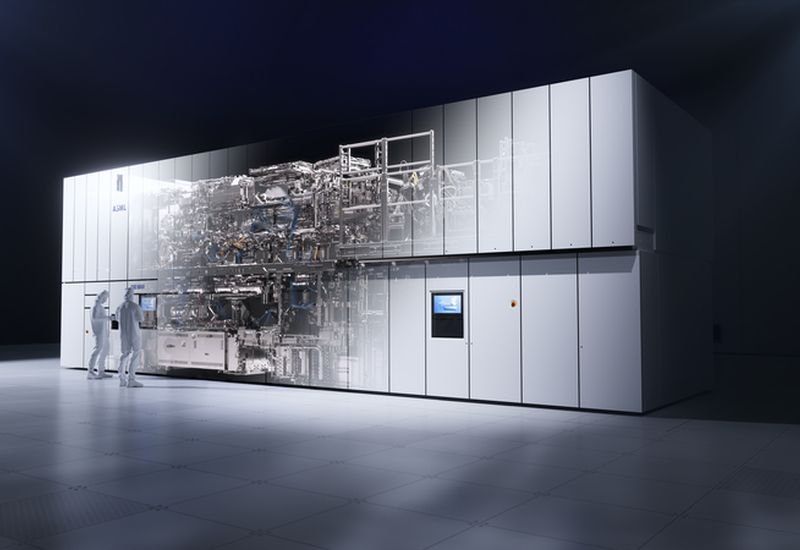

Nowy etap miniaturyzacji układów scalonych wymaga przejścia do bardziej zaawansowanych metod litografii. W najbliższych dwóch latach branża powinna uruchomić produkcję chipów przy użyciu sprzętu klasy High‑NA EUV, który pozwala osiągnąć rozmiary do 8 nm w jednym przejściu i otwiera drogę do procesów technologicznych 1,4 nm oraz poniżej 10 nm (DRAM).

1. Możliwości technologiczne High‑NA EUV

Parametr Wartość

Apertura numeryczna (NA) 0,55

Minimalny rozmiar w jednym przejściu ≤ 8 nm

Możliwe procesy technologiczne 1,4 nm (układy scalone), < 10 nm (DRAM)

Te parametry sprawiają, że urządzenia ASML Twinscan EXE:5200B i podobne rozwiązania są krytycznie ważne dla przyszłych technologii mikroelektroniki.

2. Kluczowi gracze

Firma Status wdrożenia Komentarz

ASML Producent High‑NA EUV Pierwsi klienci: Intel, Samsung, SK Hynix

TSMC Nie gotowy do masowego wykorzystania Cena jednej jednostki – 380 mln USD; planowane wycofanie chipów 1,4 nm

Intel W grudniu 2023 wprowadził Twinscan EXE:5200B Przygotowanie do wydania technologii 14A i powiązanego sprzętu

Samsung Electronics Otrzymał pierwszy skaner w grudniu 2023; drugi – w tym półroczu Planuje użycie go do Exynos 2600 (2 nm) i przyszłych procesorów Tesla

SK Hynix Zaczyna korzystać z High‑NA EUV od września 2023 Już stosuje standardową litografię EUV w DRAM (10 nm), planuje użycie co najmniej pięciu warstw EUV dla szóstej generacji

Micron Technology Jaś jeszcze nie określił terminów wdrożenia Potencjalne plany dotyczące High‑NA EUV

Rapidus (Japonia) Zaczyna technologię 2 nm; planuje 1,4 nm w 2029 Koniec 2027 powinien uruchomić masową produkcję chipów 2 nm na Hokkaido

3. Aspekty ekonomiczne

* Koszt sprzętu – jedna jednostka High‑NA EUV kosztuje około 380 mln USD.

* Przejście do droższego sprzętu podnosi koszty produkcji, co ostatecznie odzwierciedla się w cenach dla konsumentów.

* Dlatego duzi producenci (TSMC, Rapidus) zachowują ostrożność i planują wdrażanie etapowe.

4. Oczekiwane terminy

Nowe skanery litograficzne ASML do masowej produkcji zaawansowanej półprzewodnikowej technologii zaczną być aktywnie wykorzystywane w latach 2027–2028. Do tego czasu firmy będą stopniowo dostosowywać swoje linie produkcyjne, integrując High‑NA EUV z istniejącymi procesami technologicznymi.

Wniosek

Przejście do High‑NA EUV jest kluczowym krokiem w kierunku osiągnięcia rozmiarów do 1,4 nm i bardziej kompaktowych DRAM. Największe światowe podmioty już rozpoczęły prace przygotowawcze, ale masowe wdrożenie oczekuje się dopiero za kilka lat z powodu wysokich kosztów i konieczności adaptacji łańcuchów produkcyjnych.

Asted Cloud

Asted Cloud

Komentarze (0)

Podziel się swoją opinią — prosimy o uprzejmość i trzymanie się tematu.

Zaloguj się, aby komentować